Чи є єдиною метою транзисторів в ЦП виступати перемикачі, що визначають його набір інструкцій? І якщо так, то чому збільшення кількості транзисторів збільшує його швидкість?

Як збільшення кількості транзисторів в мікросхемі збільшує його швидкість?

Відповіді:

Вгорі голови:

Більше кешу , який швидше, ніж оперативна пам'ять

Більше SIMD-інструкцій , які обробляють швидше, ніж інструкції з єдиними даними

Більше ядер , тому ви можете робити дві або більше речей одночасно

Більш функціональні блоки, як вбудовані в FPU с, і кілька ALU s

Трубопроводи , тому кожне ядро може робити більше справ одночасно

Краща логіка обробки, як і більш досконала логіка прогнозування галузей

Якщо вам цікаво подібне, я дуже рекомендую книгу «Елементи обчислень » Ноама Нісана та Шимона Шоккена (принаймні, перша половина). Пройшовши його, ви зможете відповісти на власне запитання дуже детально, з повною оцінкою частин, що їх стосуються.

На веб-сайті-компаньйоні фактично є кілька прикладних глав та приміток. Це дуже доступна книга. Я пройшов це самостійно без проблем, а потім взяв абсолютно новий клас у своєму університеті, який використав його як основний текст.

Проста відповідь полягає в тому, що більше транзисторів не змушує решту з них йти швидше , але замість того, щоб робити одну справу за часовий проміжок часу, тепер ми можемо зробити два (з деякими обмеженнями).

Кен вже узагальнив деякі причини своєї відповіді . Щоб розширити це далі

- Більше кешу , який швидше, ніж оперативна пам'ять

Очевидно, що більші кеші потребують більшої кількості транзисторів. Але з більшою кількістю транзисторів ми також маємо вибір використовувати більш швидкі кеші . Кеші процесора - це просто SRAM, який, як правило, виготовляється з 6 транзисторів (AKA 6T SRAM). Однак, коли є достатньо транзисторів, можливо, варто скористатися швидшими, але більшими елементами SRAM, виготовленими з більш ніж 6 транзисторів (таких як 8T, 10T SRAM)

- Більше SIMD-інструкцій , які обробляють швидше, ніж інструкції з єдиними даними

Не тільки SIMD, але й будь-які інструкції з прискорення. Наприклад, сучасні архітектури часто мають підрозділ AES для більш швидкого шифрування / дешифрування, FMA для кращого математичного обчислення (особливо цифрової обробки сигналу) або віртуалізації для більш швидких віртуальних машин. Підтримка більше інструкцій означає, що для їх декодування та виконання потрібно більше ресурсів

- Більше ядер , тому ви можете робити дві або більше речей одночасно

- Трубопроводи , тому кожне ядро може робити більше справ одночасно

Вони цілком зрозумілі

Раніше для ФПУ не було достатньої площі відмирання, тому люди повинні придбати окрему, якщо вони мають високі вимоги до арифметики з плаваючою комою. З значно більшою кількістю транзисторів можна вбудувати FPU, значно прискоривши математику з плаваючою комою

Крім того, сучасні процесори є надзвичайними, і вони намагатимуться робити кілька речей одночасно , знаходячи незалежні фрагменти даних та обчислюючи їх раніше, хоча потік інструкцій є лінійним та послідовним. Чим більше речей вони можуть зробити паралельно, тим швидше вони будуть. Для цього ЦП може мати декілька ALU, а ALU може мати декілька одиниць виконання. Якщо, наприклад, у процесора є 5 додавачів порівняно з 4 у попередньому поколінні, то він вже працює на 25% швидше в найбільш оптимістичній ситуації без змін годинника. Більш складні процесори навіть використовують виконання поза замовленням (що стосується більшості сучасних високопродуктивних процесорів)

- Краща логіка обробки, як і більш досконала логіка прогнозування галузей

Операції, як правило, можна проводити різними способами. Якщо у вас більше транзисторів, у вас буде більше ресурсів, щоб скористатися більш швидкою технікою. Деякі прості приклади:

Біт зміщення:

Простий важіль перемикання здійснюється послідовно підключення тригерів разом.

Для цього потрібен лише один тригер за біт, отже надзвичайно компактний. Але для переміщення вліво або вправо потрібен один годинник. Ось чому мікроконтролери та невеликі вбудовані процесори мають лише вказівки щодо переміщення на одну. Подивитися

Коли у вас буде витрачено більше транзисторів, ви можете переключитися на важіль ствола . Тепер процесор може зміщувати біти за один такт з вартістю сотень чи тисяч транзисторів

Доповнення:

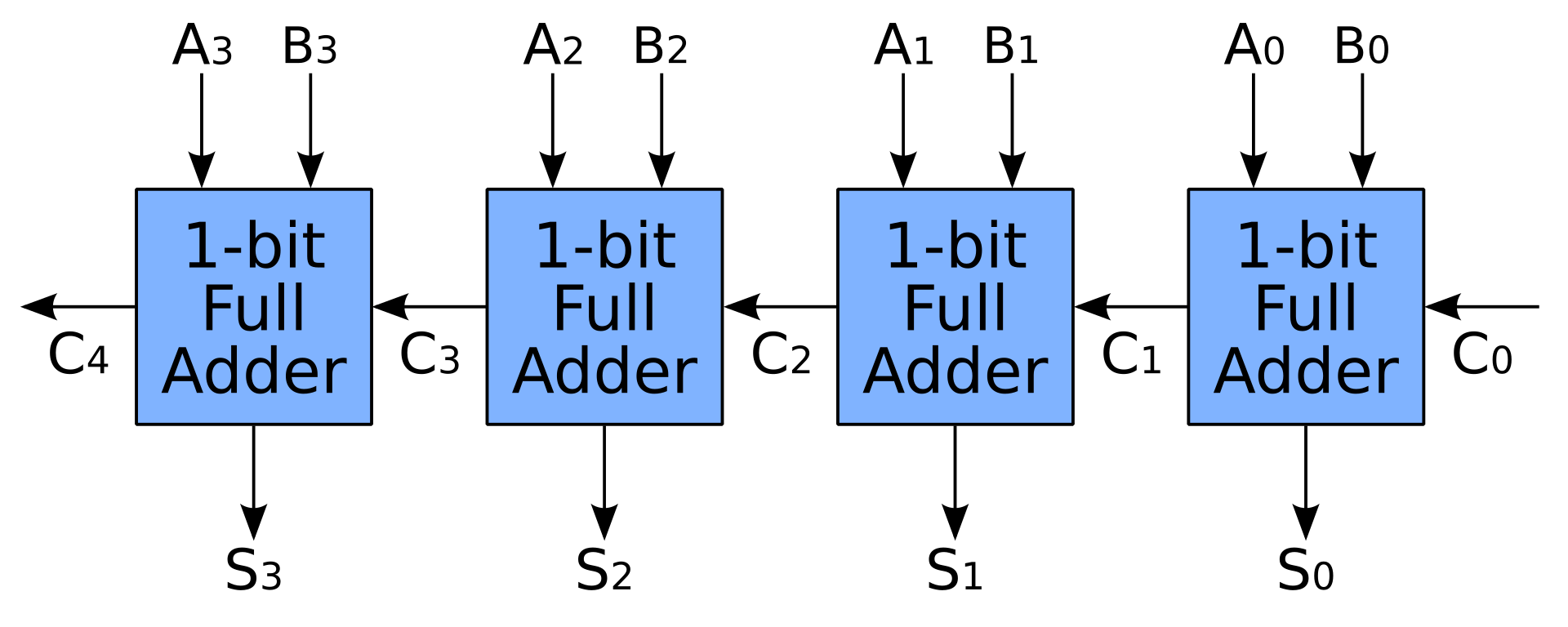

- Проста добавка виготовляється також шляхом з'єднання повних присадок послідовно. Таким чином, N-розрядний суматор потребує N годин, щоб закінчити свою роботу

- З великою кількістю транзисторів ми можемо прискорити додавання по заздалегідь обчислюючи несе з собою переносним випереджаючим переглядом або перенесення зберегти акумулятор. Повна дозатори все ще використовуються, але потрібно набагато більше місця для переносу попередньої перерахунку

- Проста добавка виготовляється також шляхом з'єднання повних присадок послідовно. Таким чином, N-розрядний суматор потребує N годин, щоб закінчити свою роботу

Те ж саме стосується інших одиниць, таких як множники, дільники, планувальник ... Наприклад, ми можемо зробити множення надзвичайно швидко за один такт, використовуючи комбінаційну логіку . Ви можете побачити кілька простих прикладів у запитанні 3-розрядних множників - як вони працюють? . Але потрібні транзистори виростуть до площі вхідної ширини, тому невеликі процесори з множником використовують замість цього послідовну логіку, щоб заощадити багато місця для множника:

Старі архітектури мультиплікаторів використовували перемикач та акумулятор, щоб підсумовувати кожен частковий продукт, часто один частковий продукт за цикл, торгуючи швидкістю для області штампу. Сучасні архітектури мультиплікаторів використовують алгоритм (Модифікований) Баф-Вулі, мультиплікатори дерев Уоллес або Тадда, щоб додати часткові продукти разом за один цикл. Продуктивність реалізації дерева Wallace іноді покращується за допомогою модифікованої Будки, що кодує один з двох мультиплікацій, що зменшує кількість часткових продуктів, які необхідно підсумувати

https://en.wikipedia.org/wiki/Binary_multiplier#Implementations

Коли у вас є величезний пул транзисторів, ви навіть можете використовувати комбінаційну логіку, щоб зробити FMA, який набагато більш ресурсоємний, ніж множник

Сучасні комп'ютери можуть містити виділений MAC, що складається з множника, реалізованого в комбінаційній логіці, з подальшим додаванням та регістром акумулятора, який зберігає результат. Вихід регістра подається назад на один вхід суматора, так що на кожен тактовий цикл висновок множника додається в регістр. Комбінаційні множники вимагають великої кількості логіки, але можуть обчислити продукт набагато швидше, ніж метод перемикання та додавання, характерний для більш ранніх комп'ютерів.